## RESEARCH ARTICLE

# Doping Effect of Pocket Implementation in MOSFET

Md. Bappi Pramanik<sup>\*</sup>, Moniruzzaman, Ahsanul Karim, and Aminur Islam Tonmoy

# ABSTRACT

This doping may be critical in MOSFET technology, which is among the most commonly used technologies in the manufacturing of electronic gadgets. Doping affects the profile of an MOSFET gate length, channel length and pocket concentration without which the functionality of an electronic device cannot be overemphasize. The specific goals of this thesis are to propose in-pocket designs for Si, Ge and GaAs. Next, we will discuss parameters such as gate length and channel length threshold voltage, pocket definitions and leakage current in semiconductors. This work requires understanding and predicting the electronic properties of doped NMOSFET and their responses to different stimuli. This thesis will thus provide good insight into the effects of doping on the electronic attributes of semiconductors. The observations recorded in this thesis include on-gate length, channel length, pocket concentration, threshold voltage, short channel impact, pocket implementation, and leakage current. Analyzing the outcomes in the controlled experiment, the authors stated the dependence between threshold voltage and atomic density, leakage current and atomic density, short channel effects and atomic density, threshold voltage and leakage current with short channel effects and the ratio between channel length and gate length.

Keywords: Atomic density, gate length and channel length, leakage current, threshold voltage.

Submitted: December 22, 2024 Published: March 24, 2025

ᡋ 10.24018/ejeng.2025.10.2.3244

University-Bangladesh (CUB), Bangladesh.

\*Corresponding Author: e-mail: bppikhn@gmail.com

# 1. Introduction

In MOSFETs, doping is defined as a process in which the manufacturer deliberately alters the properties of the semiconductor material. Investigating doping's influences on the band gap, pocket concentration, impact ionization coefficient, light absorption coefficient, and short-channel effect in semiconductors is necessary to provide an understanding of how to suppress or enhance the electronic characteristics of these materials [1]. The basic threshold voltage model as introduced in the conventional form is derived from the homogeneous doping concentration, which has been assumed to be uniform over the surface of the substrate [2]. When the MOSFET size reaches the Nano scale, short-channel effects occur [3]. The size effect causes the threshold voltage to shift, resulting in a reduced termination [4]. Doping helps in finding the lower limit voltage called the threshold voltage through which one can make a conducting path between the source and drain [5]. The threshold voltage is an essential characteristic for MOSFET devices. Having control over device manufacture is crucial [6].

Pocket implants are commonly employed in deepsubmicron CMOS technology to address short-channel effects. The primary issues using this technology are that it results into high value of load line distortion or a very significant drain induced threshold voltage change, and has low output resistance for long-channel devices. This creates this is a significant challenge for high-performance analog circuits. Thus, in this study, formulation of the first physical model of these effects is suggested. Validated here using data obtained from a 0.18 µm technology. This model is suitable for the use in SPICE modelling [7]. This Fowler said that doping of the source/drain regions, increases the depletion region of the diode and therefore decreases junction leakage current. Higher doping concentration near the drain raises GIDL value even further and this is especially true for short-channel devices [8]. When the length of the channel decreases it gives us several problems known as short channel effects. These are: drain-induced barrier lowering (DIBL), velocity saturation and threshold voltage roll-off. It may be noted that at higher doping concentrations the effect can be minimized because the channel is easier to control. These short-channel effects are found when the channel length is in the same order as the depletion-layer widths of the source and drain junction. It is shown that in the case of MOSFETs, the channel length should be larger than 2wd because of the edge effects. In other circumstances, several effects are noticed. Among the reported effects cited by several researchers at universities around the globe are: Other effects mentioned by several researchers at universities across the globe include: Offstate leakage current. If the results of impact ionization depend on these other charge carriers within a specific type of material, then that material is known as an associated material. Velocity saturation and mobility reduction; DIBL which is a drain depletion region intrusion into the channel. Drain punch through, where current flows regardless of the gate voltage situation that might emerge if the drain is at higher potential than the source leading to a depletion region around the drain extending to the source. Long-channel devices; Short-channel devices; Mobility reduction [9]. Shrinking the gate length further degrades the SCEs like DIBL and punch-through. The effects of an important device design parameter: The effects of gate length (Lg), and other key process parameters namely source/drain (S/D) doping (NSD) and channel doping (NCH) on the DC and analog/RF characteristics of gatestack based Si gate-all-around (GAA) stacked nanosheet FET structures have been studied. Analyzing the results of the above-mentioned simulation it observed that when the Lg is scaled down from 30 nm to 10 nm the short channel effects (SCEs) degrade the threshold voltage (Vth) of the device and increase the value of OFF-state current (Ioff) by nearly four orders, sub-threshold swing (SS) and drain induced barrier lowering (DIBL) is also increasing. However, as Lg is reduced, the drain current in saturation (Ion) or the ON current to the OFF current ratio (Ion/Ioff), inherent delay, and analog/RF capability improve [10].

# 2. Methodology

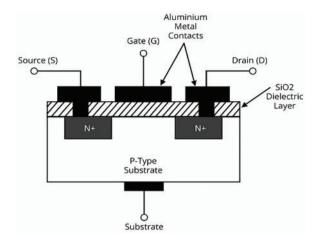

This work discusses the NMOSFET structure mentioned in the work shown in Fig. 1 below the assumed coordinate system is shown on the right side of the named structure as shown below. In particular, all the device dimensions are particularly defined from the oxide silicon interface. In the structure of the junction depth, it is a wellknown fact that the development of semiconductor devices is becoming more and more complex which in turn leads to the fact that the junction depth (rj) of such structures has to be optimized, (rj) is 30 nm.

The oxide thickness (tox) is 2.5 nm and its SiO<sub>2</sub> with a fixed oxide charge density of 1011 cm<sup>-2</sup>. The uniformly doped p-type silicon material is employed for peak at the doping concentration of  $5.25 \times 10^{17}$  cm<sup>-3</sup> [11].

# 2.1. Channel Length and Atomic Density

In semiconductor production, the tendency has been to reduce channel length as much as possible to increase the device's performance, and density and reduce its

Fig. 1. N-channel MOSFET structure.

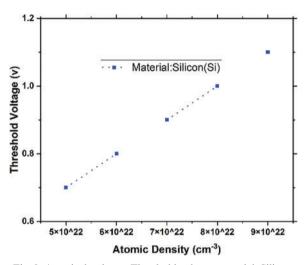

Fig. 2. Atomic density vs. Threshold voltage, material: Silicon, doping: N-type, temperature: 300 K.

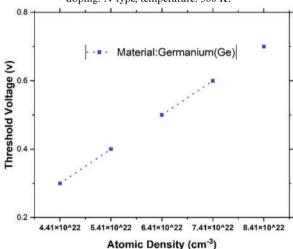

Fig. 3. Atomic density vs. Threshold voltage, material: Germanium, doping: N-type, temperature: 300 K.

power consumption. Channel length modulation is a phenomenon that is common in MOSFET transistors.

The following formula gives the channel length for a set of given parameters [12]. We show the different parameters and values in the Figs. 1-3 below when doping concentration increases (Atomic Density) for material Si, Ge, GaAs, and Channel length is decreased and use the below equation for calculating purposes:

$$\lambda = \frac{\Delta I_D}{(I_D \Delta V_D S)} \tag{1}$$

where

$\lambda$  – the channel length modulation coefficient

$\Delta I_D$  – the change in drain current

$I_D$  – the drain current

$\Delta V_D S$  – the change in drain-source voltage [12]

The following equation can be used to calculate the atomic number density (N: atoms/cm3) of a pure material having an atomic or molecular weight (M: grams/mol) and the material density (grams/cm<sup>3</sup>). This problem has been solved by:

$$N = \frac{\rho N_A}{M} \tag{2}$$

where

N – atomic number density

$\rho$  – density

$N_A - 6.0221023$  atoms or molecules per mole

$$\rho = \frac{M}{V} \tag{3}$$

where

M – atomic molecular weight

V – volume [1]

## 2.2. Gate Length and Threshold Voltage

The gate length in a MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) was defined as the actual physical length of the gate electrode or the distance between the source and drain areas. This dimension is important as the total performance of the transistor such as the speed, power used, and efficiency are implanted in this dimension [13]. The effective gate length is often given by:

$$l_g = l_{eff} + \Delta l \tag{4}$$

where

leff - Effective Gate Length

$l_g$  – the physical gate length,

$\Delta l$  – the reduction in gate length due to lateral diffusion and other short-channel effects.

The following formula calculates the threshold Voltage for a given set of parameters. The threshold voltage (V<sub>th</sub>) of a MOSFET is given by the formula:

$$V_T = V_{FB} + 2\varphi_F + \frac{\sqrt{4\varepsilon q}N_a\varphi_F}{Cox}$$

(5)

$V_T$  – the Threshold Voltage

$V_{FB}$  – the flat-band voltage

$2\phi_F$  – the Fermi potential of the semiconductor

q – the charge of an electron (1.6 × 10<sup>-19</sup> C)

NA – the acceptor doping concentration.

$\epsilon$  – the permittivity of material

Cox – the capacitance of the oxide layer

# 2.3. Leakage Current and Pocket Concentration

The following formula calculates the Leakage Current for a given set of parameters. The formula for the leakage current (I<sub>lea</sub>) in a MOSFET is given as follows

$$I_L = I_0 \times \left(\frac{e^{(V-V_0)}}{nV_T} - 1\right) \tag{6}$$

I<sub>L</sub> - Leakage Current

$I_0$  – the reverse saturation current.

V – the applied voltage.

$V_0$  – the Built-in Voltage

n – the ideality factor, typically close to one.

T – the room Temperature

*K* − the Boltzmann Constant

q – the Elementary Charge

$V_T$  – the thermal voltage.

$v_t - KT/q$

In a MOSFET, pocket concentration means doping concentration in the pocket or halo region which are near the source or drain junction. This method improves the performance of the device and helps to control the phenomena of short-channel. In general, pocket concentration is less than source/drain doping but more than channel doping concentration. Usually, the value of the pocket concentration varies in the range of (10<sup>17</sup>–10<sup>19</sup>) atoms/cm<sup>3</sup> [14]. The concept of the engineered pocket concentration helps to improve the control of the threshold voltage of the device, reduce leakage currents, and increase the general performance of the MOSFET [15]. The following formula calculates the Pocket Concentration for a given set of parameters. The formula for the Pocket Concentration  $(N_x)$  in a MOSFET is given as follows:

$$N_x = N_0 \exp\left(-\frac{x}{L}\right) \tag{7}$$

where

$N_x$  – the Pocket Concentration

X – the Distance of the Pocket

$N_0$  – the pocket doping concentration

L – the length of the doping profile

## 3. RESULT AND DISCUSSION

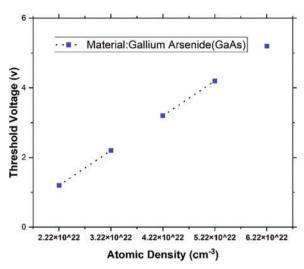

# 3.1. Atomic Density and Threshold Voltage

The given threshold voltage is higher when the doping concentration in the substrate is high. This is because a greater doping concentration corresponds to a larger depletion area charge in an NMOSFET substrate that leads to an increase in the threshold voltage, this results in more current that needs to pass through the gate voltage to change the state of the channel, reducing the on-current and the ability of the memory cell to switch quickly, and, as a bonus, reducing leakage and static power consumption. The amount of decline in performance depends on the extent to which the threshold voltage increases, which forms the important power-performance trade-off in the design. We show the different parameters and values in Figs. 12–14 below when doping concentration increases

Fig. 4. Atomic density vs. Threshold voltage, material: Gallium Arsenide, doping: N-type, temperature: 300 K.

(Atomic Density) for material Si, Ge, GaAs, Threshold voltage is also increased.

Atomic density for (Si) increases the threshold voltage for (Si) also increases. For Silicon Atomic Number Density is  $5 \times 10^{22}$  cm<sup>-3</sup> and the Threshold voltage is 0.7 v.

The equation below is found in Fig. 2:

$$y = \frac{0.7}{5 \times 10^{22}} x \tag{8}$$

Atomic density for (Ge) increases the threshold voltage for (Ge) also increases. For Germanium Atomic number Density is  $4.41 \times 1022$  cm<sup>-3</sup> and the threshold voltage is 0.3 v.

The equation below is found in Fig. 3:

$$y = \frac{0.3}{4.41 \times 10^{22}} x \tag{9}$$

Atomic density for (GaAs) increases the threshold voltage for (GaAs) also increases. For Gallium Arsenide Atomic number Density is  $2.22 \times 10^{22}$  cm<sup>-3</sup> and the threshold voltage is 1.2 v.

The equation below is found in Fig. 4:

$$y = \frac{1.2}{2.22 \times 10^{22}} x \tag{10}$$

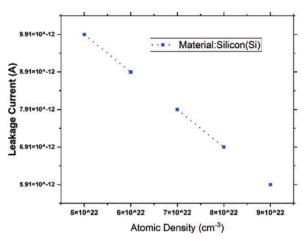

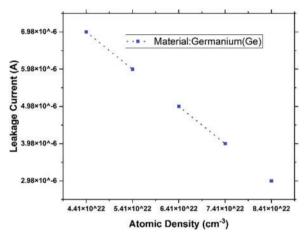

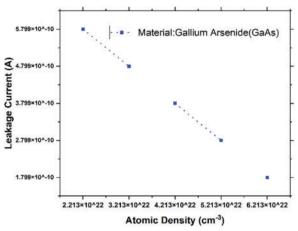

# 3.2. Atomic Density and Leakage Current

In NMOSFET increasing the atomic density reduces leakage current which is the reverse of what is observed in normal materials. This is due to the fact that high atomic density allows putting the atoms in pack, and thus there are no many defects and grain boundaries through which leakage current can flow. In its essence, the denser the material structure, the better it is at preventing undesired current flow. When the leakage current is decrease the static power consumption and good impact for deceives. We show the different parameters and values in Fig. 15 below when doping concentration increases (Atomic Density) for material Si, Ge, GaAs, Leakage Current is also decreased.

Atomic density for (Si) increases the Leakage Current for (Si) also decreases. For Silicon Atomic number Density is  $5 \times 10^{22}$  cm<sup>-3</sup> and the Leakage Current is  $5.91 \times 10^{-12}$  A.

Fig. 5. Atomic density vs. Leakage Current, material: Silicon, doping: N-type, temperature: 300 K.

Fig. 6. Atomic density vs. Leakage Current, material: Germanium, doping: N-type, temperature: 300 K.

The equation below is found in Fig. 5:

$$5 \times 10^{22} v = -1.982 \times 10^{-34} x + 4.955 \times 10^{11}$$

(11)

Atomic density for (Ge) increases the Leakage Current for (Ge) also decreases. For Germanium Atomic Number Density is  $4.41 \times 10^{22}$  cm<sup>-3</sup> and the Leakage Current is  $2.98 \times 10^{-6} \text{ A}.$

The equation below is found in Fig. 6:

$$4.41 \times 10^{22} v = -1.583 \times 10^{-28} x + 3.078 \times 10^{17}$$

(12)

$$2.213 \times 10^{22} v = -2.62 \times 10^{-32} x + 1.28 \times 10^{13}$$

(13)

Atomic density for (GaAs) increases the Leakage Current for (GaAs) also decreases. For Gallium Arsenide number Density is  $2.22 \times 10^{22}$  cm<sup>-3</sup> and the Leakage Current is  $1.799 \times 10^{-10}$  A.

The equation below is found in the graph Fig. 7.

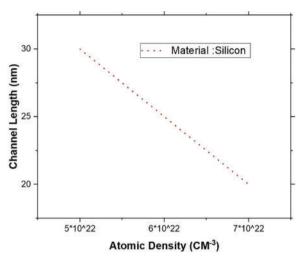

## 3.3. Atomic Density and channel length:

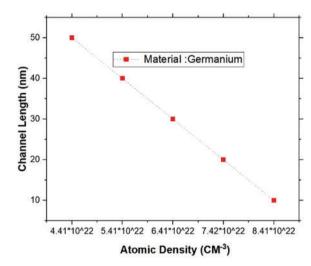

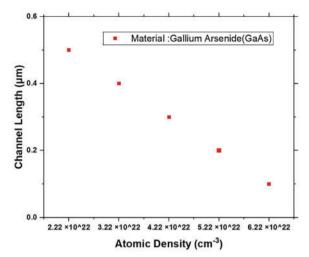

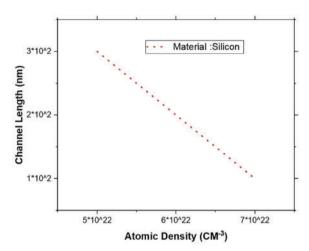

We show the different parameters and values in the Figs. 1–3, when doping concentration increases (Atomic Density) for material Si, Ge, GaAs, and Channel length is decreased.

The equation below is found in Fig. 8:

Fig. 7. Atomic density vs. Leakage Current, material: Gallium Arsenide, doping: N-type, temperature: 300 K.

Fig. 8. Atomic density vs. channel length, material: silicon, doping: N-type, temperature: 300 K.

Fig. 9. Atomic density vs. channel length, material: Germanium, doping: N-type, temperature: 300 K.

$$5 \times 10^{22} y = -4 \times 10^{-21} x + 1 \times 10^{25} \tag{14}$$

The equation below is found in Fig. 9:

$$4.41 \times 10^{22} v = -1.1338 \times 10^{-21} x + 2.205 \times 10^{24}$$

(15)

The equation below is found in Fig. 10:

Fig. 10. Atomic density vs. channel length, material: Gallium Arsenide, Doping: N-type, temperature: 300 K.

Fig. 11. Atomic density vs. gate length, material: Silicon, Doping: N-type, temperature: 300 K.

$$2.22 \times 10^{22} y = -2.703 \times 10^{-22} x + 1.332 \times 10^{22}$$

(16)

Increasing the doping concentration which means atomic density it is possible to successfully suppress the short-channel effect and control on the length of the channel. The channel length Ideal value for Silicon (Si) is 100 nm-300 nm, Germanium (Ge): 10 nm-100 nm and Gallium Arsenide (GaAs): 0.1-1 μm.

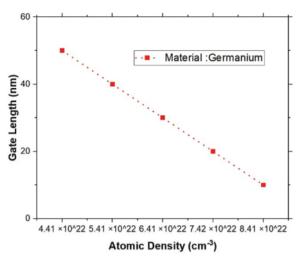

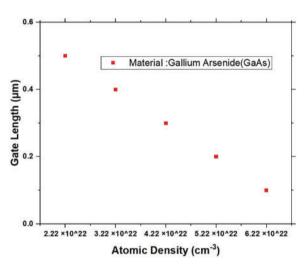

## 3.4. Atomic Density and Gate Length

We show the different parameters and values in Figs. 1– 3, when doping concentration increases (Atomic Density) for material Si, Ge, GaAs, Gate length is decrease.

The equation below is found in Fig. 11:

$$5 \times 10^{22} y = -7.2 \times 10^{-22} x + 1.8 \times 10^{24}$$

(17)

The equation below is found in Fig. 12:

$$4.41 \times 10^{22} y = -1.36 \times 10^{-21} x + 2.646 \times 10^{24}$$

(18)

The equation below is found in Fig. 13:

$$2.22 \times 10^{22} v = -2.703 \times 10^{-23} x + 1.33 \times 10^{22}$$

(19)

In today's generation MOSFETs, the gate length has been made smaller in order to enhance the operation and

Fig. 12. Atomic density vs. gate length, material: Germanium, doping: N-type, temperature: 300 K.

Fig. 13. Atomic density vs. gate length, material: Gallium Arsenide, doping: N-type, temperature: 300 K.

Fig. 14. Atomic density vs. pocket concentration, material: Silicon, doping: N-type, temperature: 300 K.

increase the number of transistors per chip. For instance, while using advanced semiconductor processes, gates can be as narrow as a few nanometers only. The Gate length Ideal value for Silicon (Si): 20 nm-50 nm, Germanium (Ge): 10 nm-100 nm and Gallium Arsenide (GaAs): 0.1  $\mu$ m-1  $\mu$ m.

Fig. 15. Atomic density vs. pocket concentration, material: Germanium, doping: N-type, temperature: 300 K.

Fig. 16. Atomic density vs. pocket concentration, material: Gallium Arsenide, doping: N-type, temperature: 300 K.

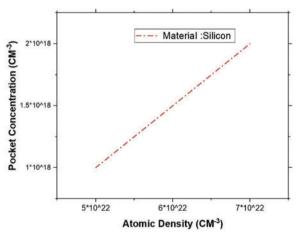

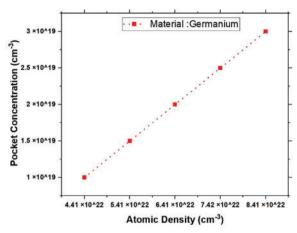

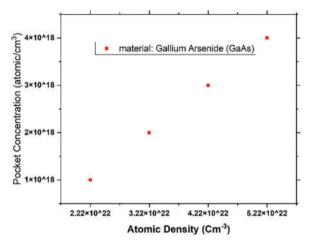

# 3.5. Atomic Density and Pocket concentration

We show the different parameters and values in Figs 9– 11, when doping concentration increases (Atomic Density) for material Si, Ge, GaAs, Pocket Concentration is also increased.

The equation below is found in Fig. 14:

$$y = \frac{1 \times 10^{18}}{5 \times 10^{22}} x \tag{20}$$

The equation below is found in Fig. 15:

$$y = \frac{1 \times 10^{19}}{4.41 \times 10^{22}} x \tag{21}$$

The equation below is found in Fig. 16:

$$y = \frac{1 \times 10^{18}}{2.22 \times 10^{22}} x \tag{22}$$

In a MOSFET, pocket concentration means doping concentration in the pocket or halo region which are near the source or drain junction. This method improves the performance of the device and helps to control the phenomena of short-channel. When atomic density increases pocket concentration also increases. The pocket concentration Ideal value for Silicon (Si):  $10^{14}$ – $10^{18}$  atomic/cm<sup>3</sup>, Germanium (Ge): 10<sup>15</sup>–10<sup>19</sup> atomic/cm<sup>3</sup> and Gallium Arsenide (GaAs):  $10^{15} - 10^{18}$  atomic/cm<sup>3</sup>.

#### 4. Conclusion

The impact of doping in pocket designs using silicon (Si), germanium (Ge) and gallium arsenide (GaAs) material forms the basis of this study. In this work we are interested in the following parameters-gate length, channel length, threshold voltage, pocket implementations, leakage current in pocket-implanted NMOSFET devices. Our main objectives are therefore as follows: As usual in such model-based studies, our primary goal can be summarized as follows: From this simulation, the results demonstrate that as the threshold voltage increases, then the performance of the device also increases. On the other hand, leakage current and short-channel effects reduce, and thus the performance of the device is improved. Further, atomic density increase in the substrate produces two significant effects; it shortens the channel length and the gate length. Nevertheless, it is worth indicating that with the increase of atomic density, the energy gap diminishes.

#### FUNDING

Self-financial support.

#### CONFLICT OF INTEREST

The authors declare that they do not have any conflict of interest.

#### REFERENCES

- Al Rakib MA, Siddik MA, Bhuiyan S, Pramanik MB. Doping effects and relationship between energy. Eur J Eng Tech Res. 2024 Jan;9(1):10–15. doi: 10.24018/ejeng.2024.9.1.3118.

- Sze SM, Lee MK. Semiconductor Device: Physics and Technology. New York: John Wiley & Sons; 1981.

- Kasai R, Yokoyama K, Yoshii A, Sudo T. Threshold-voltage analysis of short- and narrow-channel MOSFET's by threedimensional computer simulation. IEEE Trans Electron Devices. 1982 Nov;29(5):870-876.

- Mir RN, Frensley WR, Shichijo S, Blakey PA. Computational technique for probing terminal control mechanisms inside threedimensional nano-scale MOSFET. Electron Lett. 2014 Dec;50:11.

- Gaubert P, Teramoto A, Sugawa S. Impact of doping concentration on 1/f noise performances of accumulation-mode Si(100) n-MOSFETs. Japan Soc Appl Phys. 2016 Mar 8;55:45.

- Kasap SO. Electronic Materials and Devices. Canada: Vibha Mahaian: 2016.

- Kanyu Mark Cao WLXJKVKGJK. The Threshold Voltage is An Important Parameter in MOSFET Devices. Its Control. IEEE; 1999. pp. 99. doi: 10.1109/IEDM.1999.823872.

- 2008 Amirtharaiah R. www.ece.ucdavis.edu. Available from: https://www.ece.ucdavis.edu/~ramirtha/EEC216/W08/lec ture8.pdf.

- Ann Mutschler EESEIC. semiengineering.com. 2013-2024. Available from: https://semiengineering.com/knowledge\_centers/ manufacturing/process/issues/short-channel-effects/.

- [10] Jadav S, Saini G, Yadav N. The impact of key device design parameter namely gate length (Lg) and process parameters namely source/drain (S/D) doping (NSD) and channel doping (NCH) on the DC and analog/RF performance of gate-stack based Si gate-allaround (GAA) stacked nanosheet FET. Springer Nature. 2022 Jul 4;15(1):217–28. doi: 10.1007/s12633-022-01989-w.

- [11] Bhuyan MH, Ferdous F, Khosru QDM. A Threshold Voltage Model for Sub-100 nm Pocket Implanted NMOSFET. International Conference on Electrical and Computer Engineering. Dhaka, Bangladesh, 2006 Dec. doi: 10.1109/ICECE.2006.355683.

- [12] Team CA. Calculator academy. 2024 Aug 13. Available from: https://calculator.academy/channel-length-modulation-coefficientcalculator/. [Accessed 2024 Sep 19].

- [13] Timp G, Bude J, Baumann F, Bourdelle KK, Boone T, Garno J, et al. The relentless march of the MOSFET gate oxide thickness to zero. Microelectron Reliabil. 2000;40:557-562

- [14] Liu W, Jin X, Vashanth K, Green K, Krick J, Cao KM, et al. Modeling of Pocket Implanted MOSFETs for Anomalous Analog Behavior. IEEE; 1999, IEDM 99-173-174-IEDM 99.

- [15] Bhuyan MH, Khosru QDM. Inversion layer effective mobility model for pocket implanted nano scale n-MOSFET. Int J Electr Electron Eng. 2011;50-7.